90. Graphene in Chip Design: How 2D Materials Are Reshaping the Future of Semiconductors

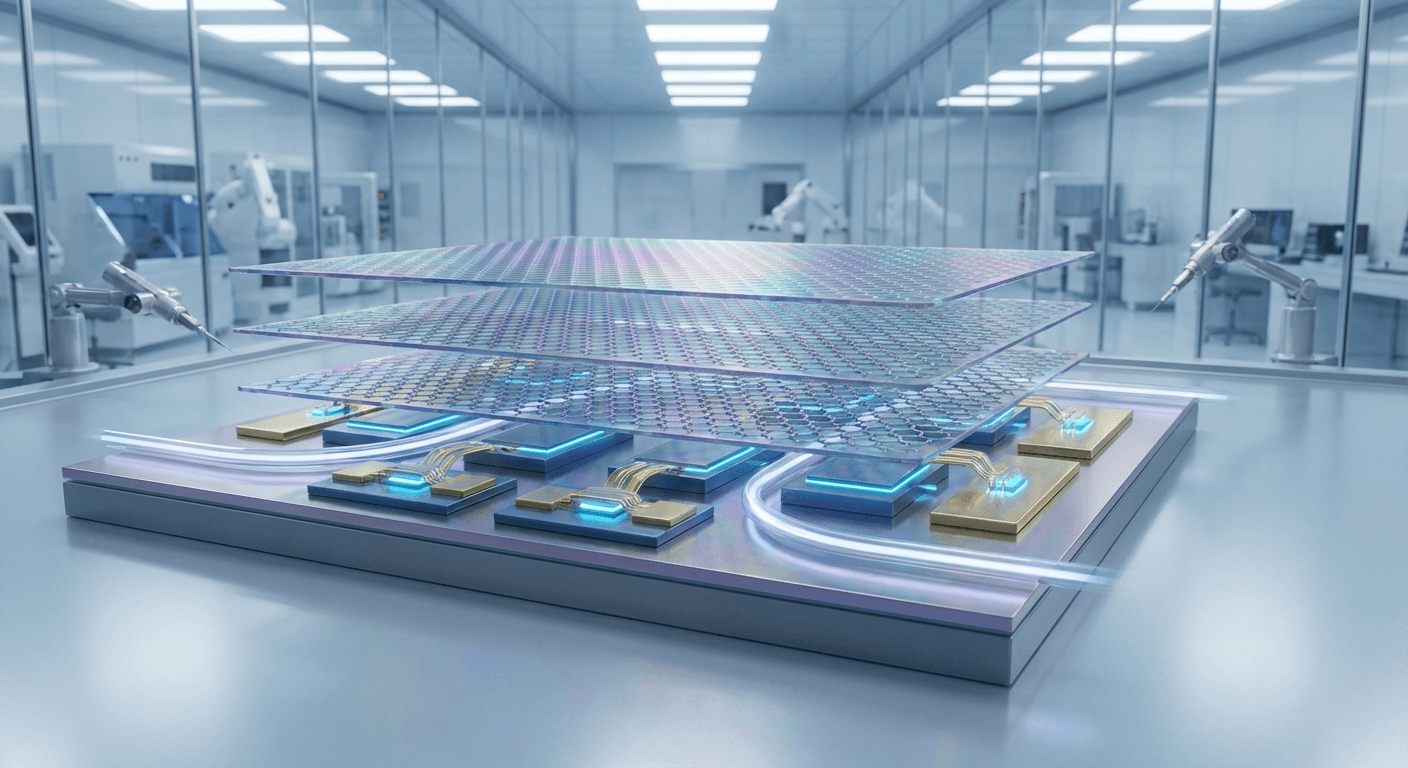

The semiconductor industry is entering a new phase where progress depends less on simple transistor shrinking and more on materials innovation, advanced packaging, and system-level architecture. For decades, silicon and copper have been the backbone of modern chips. They still dominate, but at advanced nodes the industry faces hard constraints: interconnect resistance rises, heat density increases, signal integrity gets worse, and power budgets tighten. In this context, graphene has moved from a laboratory curiosity to a serious engineering candidate for specific chip-design functions. Graphene is a two-dimensional sheet of sp2-bonded carbon atoms arranged in a hexagonal lattice. It combines high carrier mobility, very high thermal conductivity, mechanical flexibility, and atomic-scale thickness. Those properties do not automatically make it a drop-in replacement for silicon transistors. In fact, one major limitation is that pristine graphene has no natural bandgap, which makes digital logic switching difficult when high on-off ratios are required. The real opportunity is more nuanced: graphene can add value in selected layers and functions within chip systems, especially where interconnect speed, thermal spreading, RF behavior, sensing, or heterogeneous integration matter most. One of the strongest use cases is interconnect engineering. As metal lines shrink, electron scattering at surfaces and grain boundaries increases resistance, while capacitance and crosstalk penalties grow. Graphene and related 2D conductors are being explored as local interconnect materials, diffusion barriers, and contact-interface layers. Even when graphene is not the main conductor, a monolayer barrier can help suppress electromigration and diffusion in copper-based stacks. This is important because interconnect reliability, not just transistor switching speed, now limits overall chip performance in many advanced designs. Thermal management is another major bottleneck in modern chips.

Graphene's Intrinsic Properties and the Semiconductor Imperative

Graphene’s exceptional characteristics stem directly from its unique atomic structure: a single layer of carbon atoms arranged in a hexagonal lattice. This sp2-hybridized bond configuration results in a material that is both incredibly strong and remarkably light. Its electronic properties are particularly compelling for semiconductor applications, featuring exceptionally high electron mobility at room temperature, which enables electrons to travel with minimal scattering and resistance. This attribute holds significant promise for ultra-fast electronic devices where charge transport efficiency is paramount.

Beyond its electronic prowess, graphene exhibits outstanding thermal conductivity, surpassing even diamond and copper. This property is critical for managing the escalating heat generation within high-performance microprocessors and advanced packaging. Furthermore, graphene’s atomic thinness, approximately 0.34 nanometers, positions it perfectly for integration into nanoscale architectures without adding substantial bulk. Its mechanical flexibility and transparency are also valuable for emerging applications in flexible electronics and optoelectronics, further diversifying its potential impact on chip design.

The current trajectory of silicon-based integrated circuits faces fundamental physical limits as scaling approaches atomic dimensions. Traditional methods of enhancing performance by simply shrinking transistor sizes are becoming economically and physically challenging. Issues such as increased leakage currents, quantum tunneling effects, and the fundamental limitations of materials at these scales demand innovative solutions. This is precisely where two-dimensional materials like graphene offer a compelling alternative, providing a new toolkit for engineers to circumvent these roadblocks and unlock future performance gains.

Interconnect Reinvention: The Graphene Advantage

Interconnects, the microscopic "wires" that connect transistors within a chip, are increasingly becoming the primary bottleneck for overall chip performance. As these copper lines shrink to nanometer scales, their electrical resistance skyrockets due to increased electron scattering at surfaces and grain boundaries. This higher resistance translates directly into slower signal propagation, greater power consumption, and increased heat generation, undermining the gains achieved by smaller transistors. The challenge is compounded by escalating parasitic capacitance and crosstalk between adjacent lines, further degrading signal integrity.

Graphene offers a multifaceted solution to these pressing interconnect issues. Its exceptional electrical conductivity, particularly its high current carrying capacity, makes it an attractive candidate for replacing or augmenting traditional copper interconnects. While graphene’s bulk conductivity is not necessarily higher than copper, its ability to carry current in atomically thin layers with reduced electron scattering, especially in extremely narrow lines, presents a distinct advantage. Researchers are exploring its use as local interconnects within the most critical, smallest feature sizes where silicon's performance begins to falter.

Beyond direct current conduction, graphene's role as a diffusion barrier is proving revolutionary. In advanced copper metallization schemes, a barrier layer is essential to prevent copper atoms from diffusing into surrounding dielectric layers and silicon, which can cause device failure. Current tantalum nitride (TaN) barriers are relatively thick and add significant resistance. A single monolayer of graphene, being atomically thin and chemically inert, can effectively suppress copper diffusion and electromigration, offering superior performance with minimal added resistance. This not only enhances reliability but also allows for denser packing of interconnects.

Furthermore, graphene can significantly improve contact interfaces. As transistors shrink, the resistance at the interface between metal contacts and silicon becomes a dominant factor limiting device performance. Introducing a graphene monolayer at these interfaces can reduce contact resistance by creating highly efficient charge transfer pathways. This subtle but impactful integration could unlock substantial performance improvements in advanced transistors, ensuring that the benefits of smaller transistor geometries are not negated by poor contact quality. The strategic deployment of graphene in these specific layers promises a significant leap in interconnect efficiency and chip longevity.

Mastering Heat: Graphene for Thermal Management

The relentless drive for higher performance in modern computing, particularly in Artificial Intelligence (AI) accelerators, High-Performance Computing (HPC), and advanced mobile processors, has led to an exponential increase in power density. This concentration of power translates directly into immense heat generation within tiny chip areas, posing a severe threat to chip reliability and performance. Excessive heat degrades material properties, accelerates component aging, and can lead to thermal runaway, making efficient thermal management a critical frontier in chip design.

Traditional thermal solutions, relying on bulk heat sinks and thermal interface materials (TIMs) like greases and pads, are struggling to keep pace with these escalating heat loads. These materials often have limited thermal conductivity or introduce significant thermal resistance at interfaces. Graphene, with its world-leading thermal conductivity (up to 5000 W/mK for pristine samples, far exceeding copper's ~400 W/mK), presents an unparalleled opportunity to revolutionize chip cooling. Its atomic thinness allows for highly efficient heat spreading without adding substantial bulk, making it ideal for integration into extremely compact designs.

One promising application is the use of graphene as an advanced thermal interface material (TIM). By replacing traditional TIMs with graphene-based composites or films, heat can be more efficiently transferred from the hot spots on a chip to a heat spreader or cooling system. This direct and rapid heat transfer helps maintain lower operating temperatures, which extends the lifespan of components and allows chips to operate at their peak performance without throttling. The high thermal conductivity ensures that heat is quickly dissipated across a wider area, preventing localized hot spots that are particularly damaging.

Beyond TIMs, researchers are exploring graphene’s potential in integrated heat spreaders and even microfluidic cooling channels embedded directly within chip packages. Graphene’s mechanical strength and flexibility also enable the creation of robust, high-performance thermal solutions that can be precisely engineered to target specific heat-generating areas. The ability to integrate such an efficient thermal conduit directly into advanced packaging represents a transformative step towards unlocking the full performance potential of next-generation processors, making heat a manageable challenge rather than an insurmountable barrier.

Beyond the Wires: RF, Sensing, and Heterogeneous Integration

Graphene's exceptional properties extend its utility far beyond interconnects and thermal management, opening new avenues for innovation in diverse chip functionalities. Its outstanding carrier mobility makes it an ideal material for high-frequency applications, particularly in the radio frequency (RF) domain. Graphene-based RF transistors, antennas, and filters promise operation at terahertz frequencies, far exceeding the capabilities of conventional silicon devices. This potential could revolutionize wireless communication, enabling faster data rates and more compact RF front-end modules crucial for 5G, 6G, and beyond.

The atomic thinness and surface-to-volume ratio of graphene also endow it with extraordinary sensitivity, making it a prime candidate for next-generation sensing applications integrated directly onto chips. Graphene-based sensors can detect minute changes in their environment, from single molecules for biosensing to trace gases for environmental monitoring, with unprecedented precision. Its electronic properties are highly sensitive to surface adsorption, allowing for label-free detection and rapid response times. This capability could lead to "smart chips" with integrated diagnostic and monitoring functions, enhancing the intelligence and autonomy of electronic systems.

Furthermore, graphene plays a pivotal role in enabling advanced heterogeneous integration, a strategy where diverse components—processors, memory, sensors, and RF modules—are integrated into a single, high-density package. As device architectures become more complex, efficiently stacking and connecting different materials without compromising performance or reliability is crucial. Graphene's atomic thinness, mechanical flexibility, and excellent electrical and thermal properties make it an ideal interface material for bonding dissimilar components. It can facilitate efficient heat transfer between stacked dies, reduce parasitic effects, and improve overall system performance by providing robust and high-speed communication pathways between disparate functional blocks.

Overcoming Challenges: Bandgap Engineering and Scalability

Despite its remarkable properties, graphene faces specific challenges that must be addressed for widespread adoption in mainstream chip manufacturing. The most significant limitation for digital logic applications is its lack of a natural bandgap in pristine form. A bandgap is essential for transistors to effectively switch between an "on" and "off" state with a high current ratio, enabling clear distinction between logic 0 and logic 1. Without a bandgap, graphene transistors exhibit poor on-off ratios, making them unsuitable for traditional digital switches.

Researchers are actively pursuing several strategies to engineer a bandgap into graphene. One promising approach involves fabricating graphene nanoribbons (GNRs), where confining the material to widths of a few nanometers induces a bandgap through quantum confinement effects. The bandgap in GNRs is inversely proportional to their width, allowing for tunability. Other methods include applying strain, chemical doping, or creating bilayer graphene structures with an applied electric field, each offering different levels of bandgap control and compatibility with existing fabrication processes. While these methods show promise, achieving consistent and scalable bandgap engineering remains a complex area of research.

Beyond fundamental material properties, the scalability and manufacturability of graphene present significant hurdles. Producing high-quality, large-area graphene sheets consistently and cost-effectively is crucial for industrial adoption. Current methods like Chemical Vapor Deposition (CVD) have made progress in large-area synthesis, but integrating these processes into existing semiconductor fabrication lines requires substantial engineering effort. Challenges include minimizing defects, ensuring uniform thickness, and developing reliable transfer techniques to place graphene precisely onto target substrates without damage or contamination.

Ensuring the long-term reliability and stability of graphene-integrated devices under various operating conditions, including high temperatures and electrical stress, is another critical aspect. Standardization of manufacturing processes, quality control, and testing protocols will be vital for industry confidence and widespread commercialization. Overcoming these scientific and engineering challenges demands continued investment in research and development, fostering collaboration between academic institutions and semiconductor industry leaders.

The Road Ahead: Research, Development, and Market Adoption

The journey of graphene from a laboratory discovery to an industrial cornerstone in chip design is a complex but increasingly promising one. Current research focuses on refining bandgap engineering techniques to improve graphene's suitability for logic applications, while simultaneously enhancing the scalability and quality of large-area graphene synthesis. Breakthroughs in direct growth methods on dielectric substrates and advanced transfer techniques are crucial for seamless integration into existing silicon-based manufacturing processes. These efforts are aimed at reducing costs and improving manufacturing throughput.

Industry partnerships are accelerating the transition of graphene from academic research into practical applications. Major semiconductor companies are actively exploring graphene's potential, often in collaboration with specialized graphene producers and research consortia. Pilot projects are underway to validate graphene's performance in specific chip functions, such as high-performance interconnects and advanced thermal solutions. These real-world evaluations are critical for demonstrating the material’s reliability and economic viability at an industrial scale, moving beyond theoretical benefits to tangible results.

While a complete replacement of silicon by graphene across all chip functions is not the immediate future, its strategic integration into specific layers and components is gaining traction. The focus remains on leveraging graphene where its unique properties offer the most significant performance advantages and address critical bottlenecks that silicon cannot overcome. This includes areas like ultra-fast RF front ends, highly sensitive on-chip sensors, and particularly in the most challenging aspects of interconnects and thermal management for advanced processors.

The widespread market adoption of graphene in chip design is likely to be an evolutionary process, beginning with niche high-performance applications and gradually expanding as manufacturing techniques mature and costs decrease. We anticipate a phased introduction, starting with passive components and interface layers, then moving towards more active device integration. The next decade will be pivotal in establishing graphene as an indispensable material, fundamentally reshaping the future of semiconductor technology and enabling the next generation of computing.

FAQ

What is the primary limitation of graphene for traditional digital transistors?

The main limitation is that pristine graphene lacks a natural bandgap. A bandgap is necessary for a transistor to effectively switch between "on" and "off" states with a high ratio, which is fundamental for digital logic operations.

How does graphene help with interconnect challenges?

Graphene helps by offering high current carrying capacity in atomically thin lines, reducing electron scattering. It can serve as a diffusion barrier to prevent copper migration and electromigration, and improve contact resistance at metal-semiconductor interfaces, enhancing overall reliability and performance.

Why is graphene considered a superior material for thermal management?

Graphene boasts exceptionally high thermal conductivity, significantly higher than traditional materials like copper or diamond. Its atomic thinness allows for efficient heat spreading from hot spots without adding bulk, which is critical for cooling high-power density chips and extending device lifespan.

Can graphene replace silicon entirely in future chips?

No, a complete replacement of silicon is not the immediate or likely future. Graphene's greatest potential lies in its strategic integration for specific functions where its unique properties provide significant advantages, such as interconnects, thermal management, RF components, and advanced sensors, complementing rather than replacing silicon.

What are the main manufacturing challenges for integrating graphene into chips?

Key challenges include the scalable production of high-quality, large-area graphene sheets, developing reliable and damage-free transfer techniques onto various substrates, and ensuring process compatibility with existing semiconductor fabrication infrastructure. Overcoming these hurdles is crucial for cost-effective industrial adoption.

Conclusion

The evolution of the semiconductor industry has reached a pivotal juncture, where incremental scaling of silicon is no longer sufficient to meet the escalating demands of modern computing. This new era mandates a profound shift towards materials innovation, advanced packaging, and novel architectural approaches. Graphene, a material once confined to research laboratories, has decisively emerged as a critical enabler for this transformation, offering a unique combination of electrical, thermal, and mechanical properties that directly address the most formidable challenges in chip design.

From revolutionizing interconnects by combating resistance and electromigration, to masterfully managing the intense heat generated by high-performance processors, graphene provides solutions where traditional materials falter. Its potential extends further into high-frequency RF applications, ultra-sensitive on-chip sensing, and facilitating robust heterogeneous integration. While the challenge of bandgap engineering for digital logic remains an active research area, the strategic deployment of graphene in specific, high-impact functions promises to unlock unprecedented levels of performance and efficiency across the entire chip ecosystem.

The journey towards widespread adoption involves continued scientific breakthroughs in synthesis and integration, coupled with robust industry collaboration and standardization. Graphene is not merely an incremental improvement; it represents a fundamental re-imagining of what is possible within the confines of a microchip. As we advance, graphene will play an indispensable role in shaping the next generation of semiconductors, driving innovation that extends the boundaries of computing and powers the future of technology.