applications

Graphene in Chip Design: How 2D Materials Are Reshaping the Future of Semiconductors

The semiconductor industry is entering a new phase where progress depends less on simple transistor shrinking and more on materials innovation, advanced packaging, and system-level architecture. For decades, silicon and copper have been the backbone of modern chips. They still dominate, but at advanced nodes the industry faces hard constraints: interconnect resistance rises, heat density increases, signal integrity gets worse, and power budgets tighten. In this context, graphene has moved from a laboratory curiosity to a serious engineering candidate for specific chip-design functions.

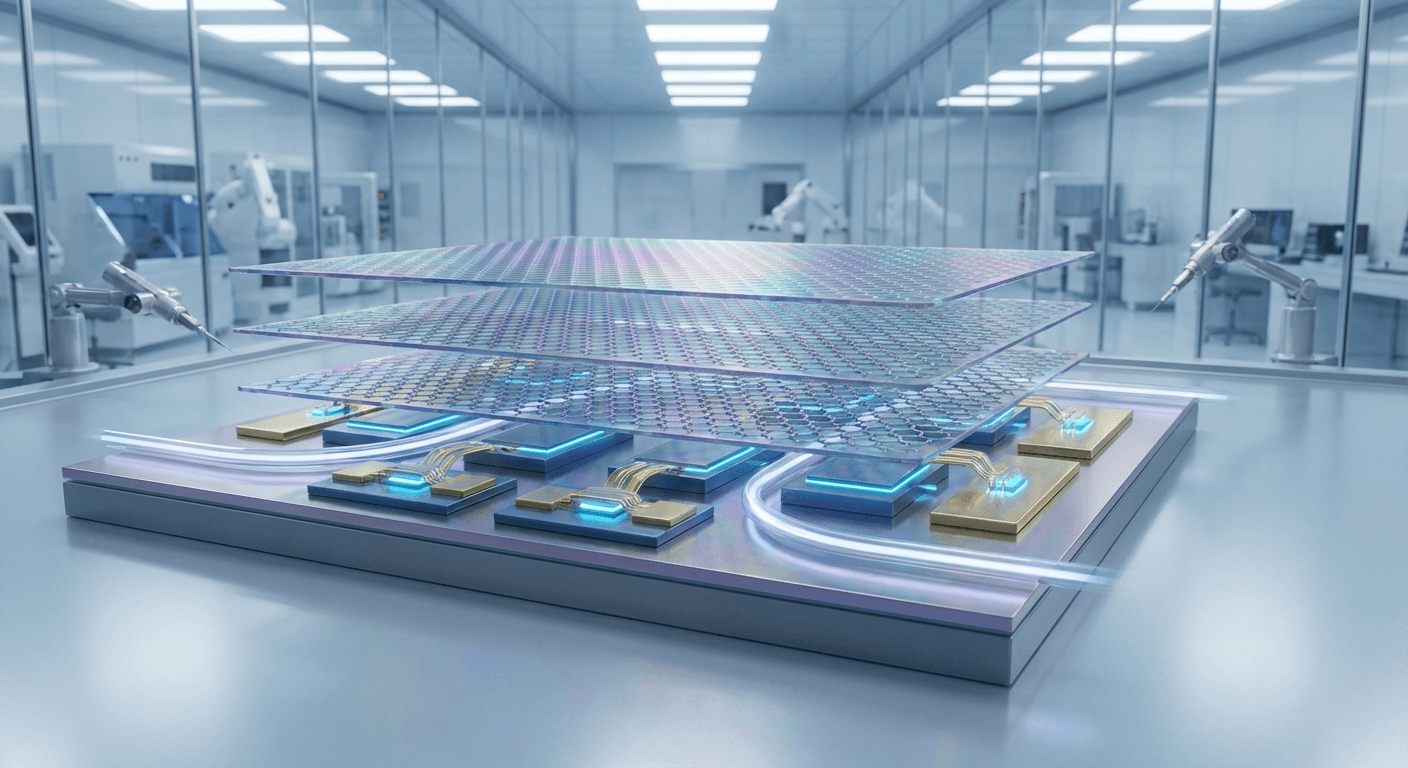

Graphene is a two-dimensional sheet of sp2-bonded carbon atoms arranged in a hexagonal lattice. It combines high carrier mobility, very high thermal conductivity, mechanical flexibility, and atomic-scale thickness. Those properties do not automatically make it a drop-in replacement for silicon transistors. In fact, one major limitation is that pristine graphene has no natural bandgap, which makes digital logic switching difficult when high on-off ratios are required. The real opportunity is more nuanced: graphene can add value in selected layers and functions within chip systems, especially where interconnect speed, thermal spreading, RF behavior, sensing, or heterogeneous integration matter most.

One of the strongest use cases is interconnect engineering. As metal lines shrink, electron scattering at surfaces and grain boundaries increases resistance, while capacitance and crosstalk penalties grow. Graphene and related 2D conductors are being explored as local interconnect materials, diffusion barriers, and contact-interface layers. Even when graphene is not the main conductor, a monolayer barrier can help suppress electromigration and diffusion in copper-based stacks. This is important because interconnect reliability, not just transistor switching speed, now limits overall chip performance in many advanced designs.

Thermal management is another major bottleneck in modern chips. AI accelerators, high-end CPUs, and RF front-end modules all face localized hotspots. Graphene is attractive here because of its excellent in-plane thermal conductivity. Designers can use graphene-enhanced thermal interface materials, heat-spreading films, or composite layers in package-level stacks. The practical goal is straightforward: reduce peak junction temperatures, smooth thermal gradients, and preserve timing/power stability under burst workloads. Even modest thermal improvements can translate into measurable gains in sustained performance and component lifetime.

Graphene is also promising for analog and RF electronics. Unlike digital CMOS logic, RF circuits can benefit from high carrier mobility and high-frequency response even without a large bandgap. Graphene-based transistors and tunable components have shown potential for mixers, modulators, detectors, and high-speed communication elements. In chip design terms, this means graphene may first scale where analog behavior, high-frequency operation, and reconfigurability matter more than strict digital on-off logic.

Photonic-electronic integration is another frontier where graphene can play a meaningful role. Silicon photonics is mature but constrained by fixed material behavior and specific process assumptions. Graphene can be integrated as an electro-optic tuning layer in waveguide structures, enabling modulators and switches at telecom wavelengths such as 1550 nanometers. That enables compact optical interconnect functions and potentially lower-energy data movement between compute blocks. As data-center and AI workloads push bandwidth requirements upward, these hybrid photonic architectures become increasingly relevant.